PCIŒÓĂÜĐŸÆŹ

PCIEŒÓĂÜĐŸżš

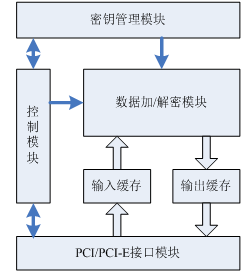

žßĐÔÄÜPCI/PCI-EœÓšżÚŒÓœâĂÜĐŸÆŹŁŹÊÇżîÍšÓĂ”ÄĂÜÂëÔËËăĐŽŠÀíÆśŁŹÄÚǶžßĐÔÄÜÓČŒțĂÜÂëÔËŠÎËăÄŁżéŁŹžĂĐŸÆŹÊÇżîÍ»

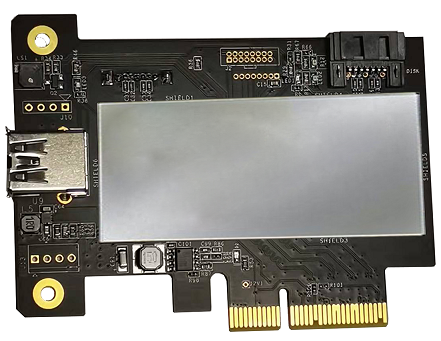

·ąÄŁÊœÊ”ÏÖĄïŽóÊęŸĘżé”ČӜâĂÜÔËË㥣ÓÉÓÚČÉÓĂÁËÍšÓĂ”ÄPCI/PCI-E”ÄŸÖČżšKŚÜÏßœÓżÚŁŹżÉÒÔ·œ±ă”ŰǶÈ딜žśÖÖĐÎÊœĄû”ÄŒÆËă

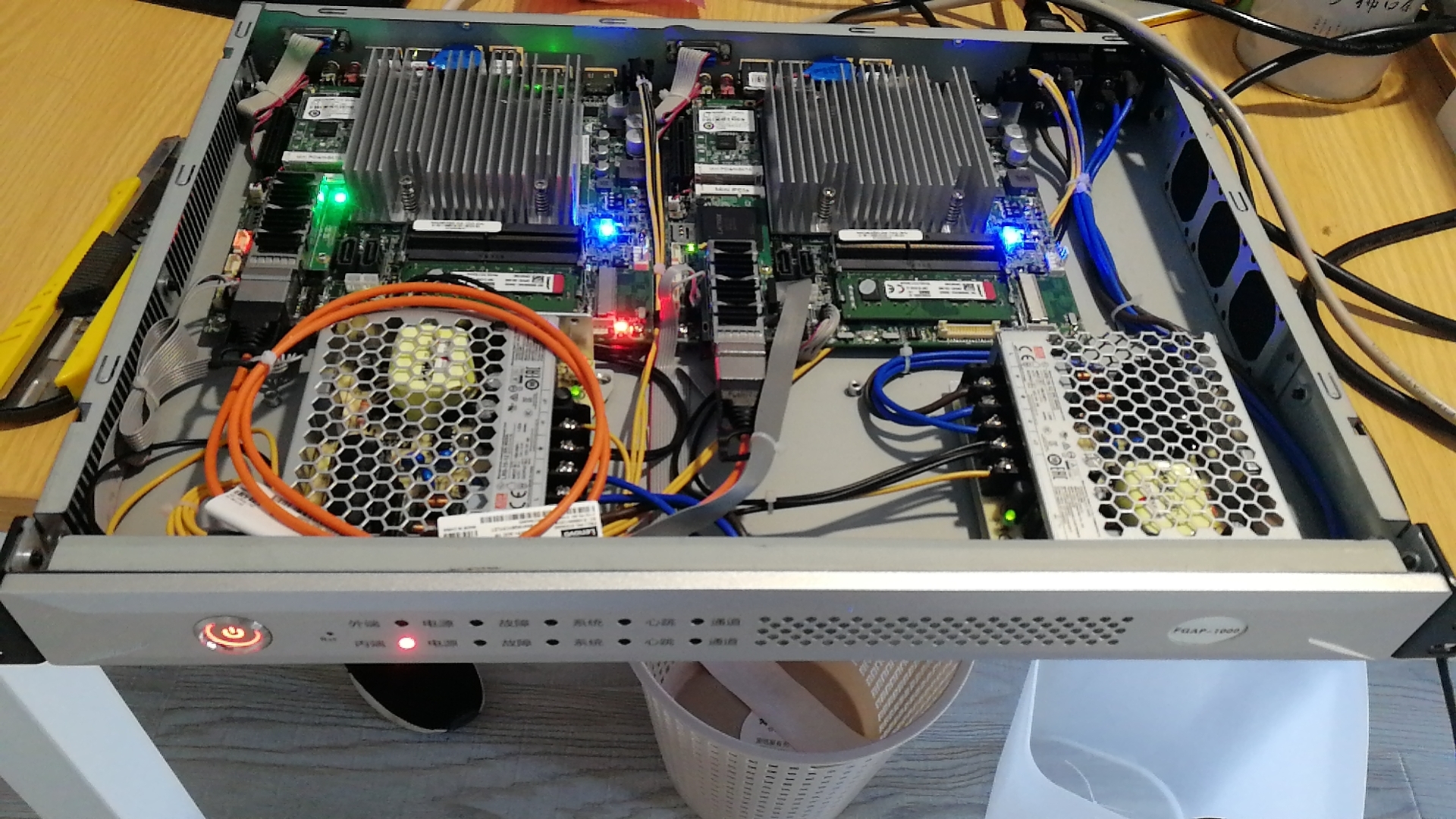

»úÏ”ÍłÖĐŁŹÈçPC»úĄą±ÊŒÇ±ŸĄąžśÖÖ·țÎńÆśșÍžśÖÖŐÆÉÏ”çŚÓÉ豞”ÈĄŁ

ĐŸÆŹÎąÌćÏ”œášvččÈçÍŒ1ËùÊŸŁș

ÍŒ1 ĐŸÆŹÎąšÌćÏ”œáččÍŒ

ÄÚČżÂßŒÄŁżéÖśÒȘÓÉŁșA)ÊęŸĘŒÓœâĂÜÄŁżéŁ»B)ĂÜÔżčÜÀíÄŁżéŁ»C)żŰÖÆÄŁżéŁ»D)ŚÜÏßœÓżÚÄŁšKżéŚéłÉĄŁ

ÊęŸĘÍš”ÀÓĐŁș

A)Öś»úÍščęPCI/PCI-EœÓżÚŁŹœ«ÒȘŒÓ/œâĂÜ”ÄÊęŸĘÖĂÈëÊäÈë»șŽæÖĐŁŹÊęŸĘŒÓ/œâĂÜÄŁĄïżéÔÚżŰÖÆÄŁżé”ÄżŰÖÆÏÂÍêłÉŒÓ/œâĂÜ

ÔËË㣏ȹœ«ÔËËășĂ”ÄÊęŸĘÖĂÈëÊäłö»șŽæÖĐŁŹPCI/PCI-EœÓżÚÄŁżéŚîÖŐœ«ÊęŸĘ·”»Ű”œÖś»úÄÚŽæÖĐŁ»

B)Öś»úÍščęPCI/PCI-EœÓżÚÏòżŰÖÆÄŁżé·ąłöÖžÁżŰÖÆ»ò¶ÁÈĄ”±Ç°ŒÓ/œâĂÜÄŁżéșÍĂÜÔżčÜÀíÄŁżé”ÄÔËĐĐÓëŚŽÌŹŁ»

C)ĂÜÔżčÜÀíÄŁżéÓëĐŸÆŹÍâČżUSBœÓżÚĐÍ»òÖÇÄÜżšĐÍĂÜÔż”ÄĂÜÔżÔŰÌćÏໄĆäșÏŁŹœűĐĐĂÜÔż”ÄčÜÀíŁŹžșÔđÊęŸĘŒÓ/œâĂÜÄŁżé

ËùÓĂĂÜÔż”ÄÉúłÉĄąŃéÖ€ĄąŽæŽąșÍł·Ïú”ÈĄŁ

ÌŰ”ă

2 ČÉÓÿɌÛșÏĄążÉžŽÓĂ”ÄVerilog-HDLÓïŃÔÉèŒÆŁŹ·œ±ăŚöłÉŚšÓĂŒŻłÉ”ç·Ł»

2 ČÉÓĂ”„ʱÖÓÍŹČœ”ÄÂߌÉèŒÆŁŹĐŸÆŹÖÆłÉŒò”„ĄąłÉ±Ÿ”ÍŁ»

2 PCIŚÜÏßœÓżÚŚńŃčæ·¶2.2ŁŹŚÜÏßÊęŸĘżí¶ÈÎȘ32λŁŹÊ±ÖÓÆ”ĄőÂÊÎȘ66MHzŁŹ”„čŠÄÜŁŹżÉ而śĄőĄĄÔÚÖś/ŽÓ·œÊœŁ»

2 PCI-EŚÜÏßœÓżÚŚńŃčæ·¶2.0ŁŹČÉÓĂ4X”ÄœÓżÚÄŁÊœŁ»

2 ÎȘÁ˱ŁÖ€ŚÜÏßÖźŒä”ÄžßËÙÊęŸĘŽ«Ê䣏ČÉÓĂŽóÈĘÁż”ÄË«żÚÍŹČœSRAMŚśÎȘFIFOŁ»

2 ÄÚǶžßĐÔÄÜÓČŒÓ/œâĂÜÔËËăÄŁżéŁŹÖ§łÖÈçSM4ĄąDESĄąTDESșÍAES”È¶ÔłÆŒÓĂÜËă·šŁ»

2 ÒČšèżÉÒÔÄÚǶ»òÍâčÒŁŹč«żȘĂÜÔżËă·šŁšÈçSM2ĄąRSAșÍECC”ÈŁ©ÄŁżé»òÌ۶ščúÄÚšËă·šŁ»

2 ÄÚǶ8051ÎążŰÖÆÆśŁŹÓĂÓÚ¶ÔÖÇÄÜżšĂÜÔż”ÄčÜÀíŁ»

2 ÀûÓĂPCI ROMłÌĐòŁŹÊ”ÏÖÓĂ»§żÚÁî”ÄÈÏÖ€ŁŹÊ”ÏÖżȘ»úÒȘÓĐĂÜÔżșÍżÚÁ

2 Ö»ÓĐÍščęÓĂ»§żÚÁî”ÄŃéÖ€ŁŹœâĂÜŽŠÀíÆśČĆÄÜŒÓÔŰĂÜÔżŁŹ»úÆśČĆÄÜÆô¶ŻŁ»

2 șŹÓĐXOR FlashżŰÖÆœÓżÚŁŹżÉÒÔÊ”ÏÖROM”ÄλÖĂŁ»

2 ÊÊÓĂÓÚ̚ʜ»úĄą·țÎńÆśĄą±ÊŒÇ±ŸșÍžśÖÖÒƶŻŒÆËăÍšĐĆÉ豞”ÈĄŁ